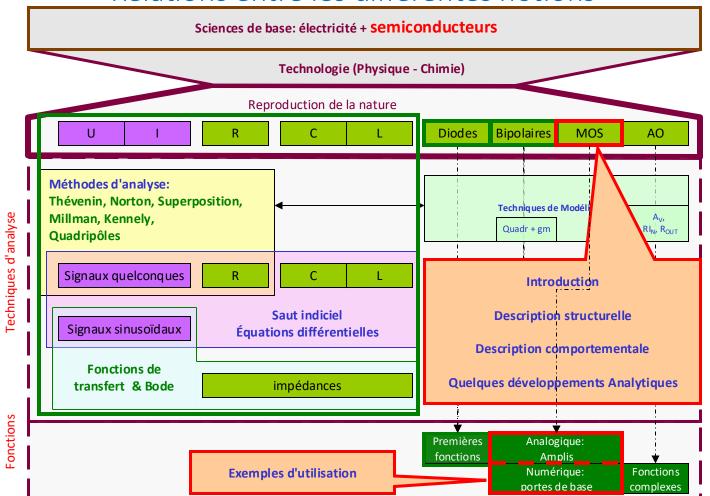

### Relations entre les différentes notions

### Introduction

#### **Avant**

Transistor à effet de champ:

- Connu bien avant le bipolaire

Technologie difficile à maîtriser

$-V_{T}$

Réponse en fréquence loin d'atteindre les performances actuelles

- très dépendante des dimensions géométriques

- du processus de fabrication

#### Actuellement

Technologie MOS mieux maîtrisée

Technologie MOS supplante Bipolaire:

- Circuits logiques intégrés VLSI

- Certaines fonctions analogiques.

# Avantages du MOS vis-à-vis du bipolaire

| Coût technologique  | Structure très simple (plusieurs milliards de transistors sur 1 puce) |

|---------------------|-----------------------------------------------------------------------|

|                     | Surface réduite                                                       |

|                     | Isolation naturelle                                                   |

|                     | - Composants vis-à-vis des composants voisins,                        |

|                     | - Pas de "caissons d'isolation »                                      |

|                     | Limitation du nombre d'étapes de fabrication                          |

| Coût de conception  | Structure très simple (bis)                                           |

| Coût d'exploitation | Consommation très faible                                              |

|                     | - En particulier pour les circuits CMOS                               |

|                     |                                                                       |

| Divers              | Très haute impédance d'entrée.                                        |

|                     | Possibilité de réaliser des fonctions complexes                       |

|                     | - Moins de composants que les bipolaires                              |

|                     | - Exemple : les mémoires dynamiques                                   |

|                     |                                                                       |

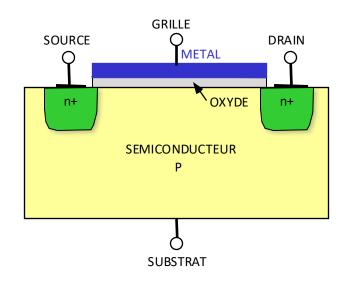

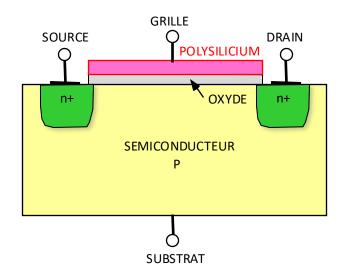

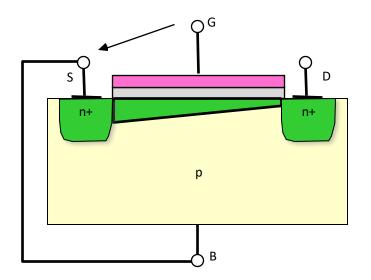

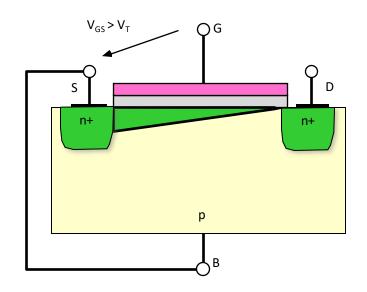

## Description structurelle

MOS : Metal Oxide Semiconductor Grille Metal ou Polysilicium

# Caractéristiques électriques

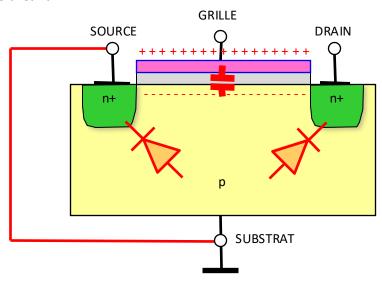

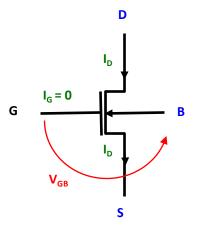

#### MOS à Canal N

- Oxyde fin

- Capacité ---> I<sub>G</sub> = 0

- Dispositif symétrique

- Diodes polarisées en inverse

- Souvent, Source reliée au substrat

## Principe de fonctionnement

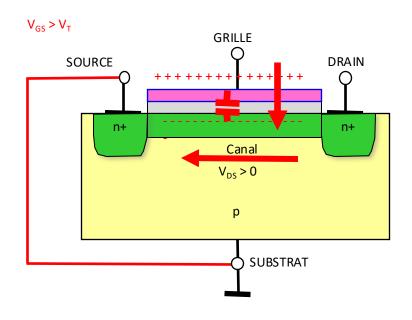

#### Principe

- $V_{GB} > V_{T}$

- Accumulation de charge à l'interface SiO<sub>2</sub>

- Apparition d'un canal N

- Champ électrique entre Drain et Source

- Champ V<sub>DS</sub> implique courant I<sub>DS</sub>

- Déplacement d'électrons dans le Canal N

- Courant I<sub>DS</sub>

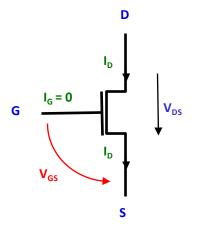

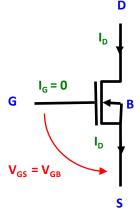

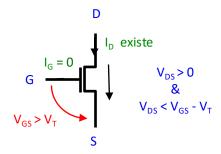

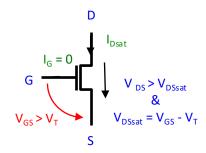

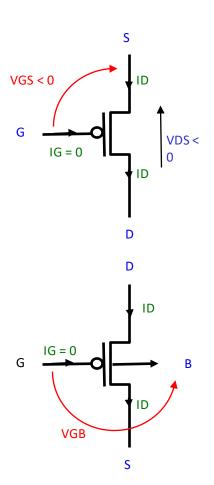

# Symbole électrique d'un transistor MOS à canal n

Substrat non représenté si au même potentiel que la source

Trois modes différents de fonctionnements

Vision très épurée

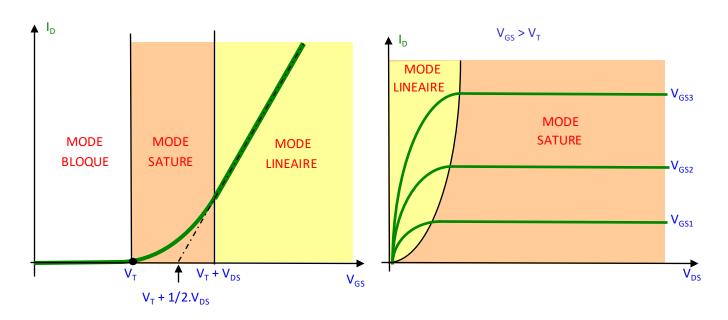

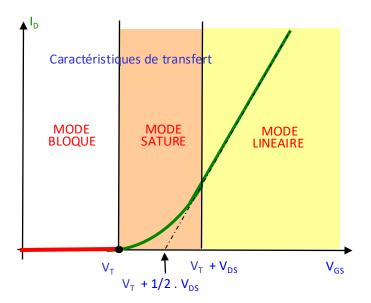

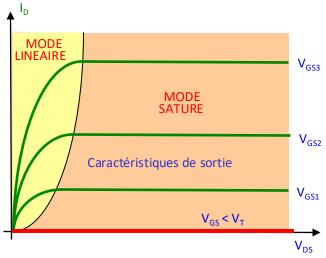

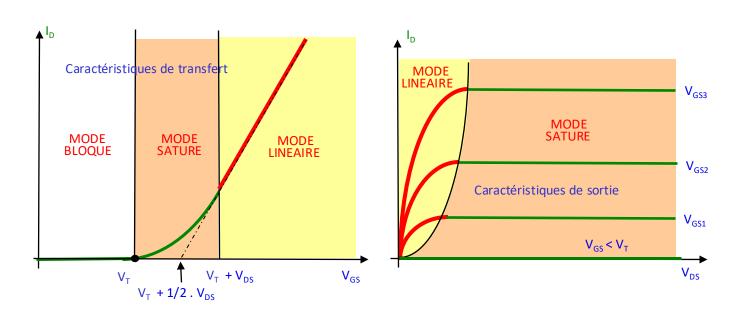

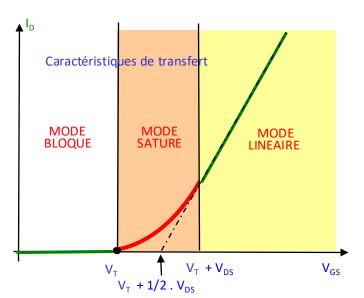

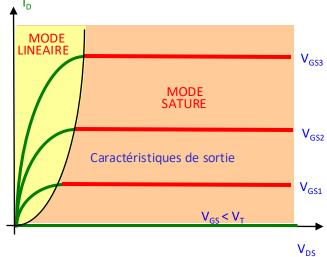

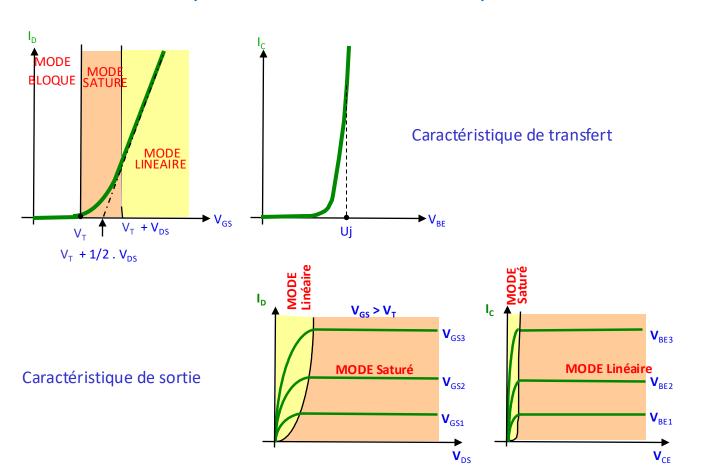

# Observation des caractéristiques

Caractéristique de transfert

Caractéristique de sortie

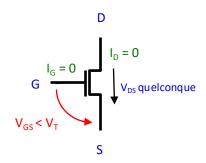

## Le mode bloqué

$V_{GS} = V_{GB}$  est inférieure à  $V_{T}$  (-2V ..... 2V)

• Pas d'apparition du canal.

#### MOS ne conduit aucun courant

• (idem bipolaire)  $I_D = 0$

# Le mode linéaire (ou mode de conduction)

$$V_{GS} > V_T \& V_{DS} < V_{DSsat} = V_{GS} - V_T$$

Canal non uniforme entre source et drain.

#### Le transistor conduit

I<sub>D</sub> = ? (augmente avec la tension V<sub>DS</sub>)

# MOST en régime linéaire (linear mode)

$$V_{GS} > V_{T}$$

&  $0V < V_{DS} < V_{DSsat} = V_{GS} - V_{T}$

$$I_D = K. V_{DS}. \left( V_{GS} - V_T - \frac{V_{DS}}{2} \right)$$

$$K = \mu. C_{OX}. \frac{W}{L}$$

K = transconductance du MOST en A/V<sup>2</sup> ou  $\mu$ A/V<sup>2</sup>, f(technologie, dimensions du MOS)

$\mu = mobilité$  des porteurs (- pour N-MOST et + pour P-MOST)

Pas de PINCH-OFF (pincement) du canal dans ce mode

### Le mode saturé

$$V_{GS} > V_T \& V_{DS} > V_{DSsat} = V_{GS} - V_T$$

- Canal existe avec pincement côté drain

- $V_{DSsat}$  varie avec  $V_{GS}$  et vaut:  $V_{DSsat} = V_{GS} V_{T}$

#### Le transistor conduit

• I<sub>D</sub> = ? (augmente avec la tension V<sub>DS</sub>)

# MOST en régime saturé (saturation mode)

$$V_{DS} > V_{DSsat}$$

ou

$$V_D > V_{Dsat}$$

PINCH-OFF (Pincement) du canal côté Drain Le courant ne varie plus avec  $V_{DS}$

$$I_D = \frac{K}{2} \cdot (V_{GS} - V_T)^2$$

# Comparaison MOS & bipolaire

## Résumé

#### Caractéristiques de sortie:

Mode linéaire vers mode saturé avec V<sub>DS</sub> croissantes

#### Caractéristique de transfert:

Mode saturé vers mode linéaire avec V<sub>GS</sub> croissantes

#### Mode saturé:

$$V_{DS} > V_{DSsat}$$

$V_{DS} > V_{GS} - V_{T}$  ou  $V_{GS} < V_{DS} + V_{T}$

$I_{D} = \frac{K}{2} \cdot (V_{GS} - V_{T})^{2}$

#### Mode linéaire :

$$\begin{vmatrix} V_{DS} < V_{DS \text{sat}} \\ V_{DS} < V_{GS} - V_{T} \quad \text{ou } V_{GS} > V_{DS} + V_{T} \end{vmatrix} I_{D} = K. V_{DS}. \left( V_{GS} - V_{T} - \frac{V_{DS}}{2} \right)$$

## Caractéristiques électriques du p-MOS

Le mode **BLOQUE**:  $V_{GS} > V_T \& I_D = 0$

Le mode LINEAIRE :  $V_{GS} < V_{T} \& V_{DS} > V_{DSsat}$

$$I_D = K.V_{DS} (V_{GS} - V_T - 1/2 V_{DS})$$

Le mode *SATURE*: V<sub>GS</sub> <V<sub>T</sub> et V<sub>DS</sub> <V<sub>DSsat</sub>

$$I_D = K/2 (V_{GS} - V_T)^2$$

Tension de seuil V<sub>T</sub> négative.

La tension de saturation V<sub>DSsat</sub> est aussi négative:

$$V_{DSsat} = V_{GS} - V_{T}$$

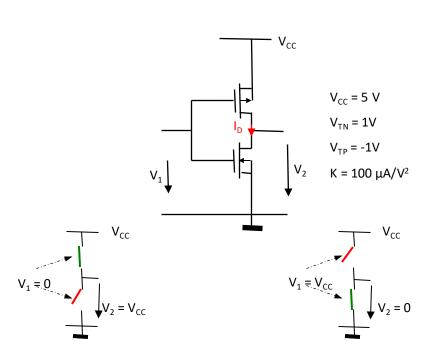

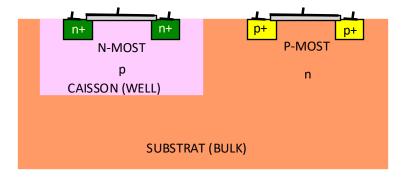

# La technologie CMOS

Complementary Metal Oxide Semiconductor

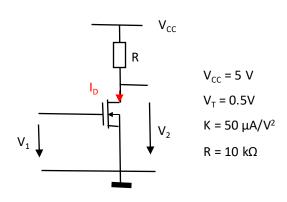

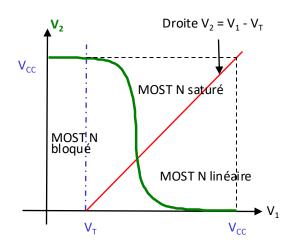

## **EXERCICE 1**

Inverseur logique N-MOS

Calculer et tracer la caractéristique de transfert  $V_2 = f(V_1)$ .

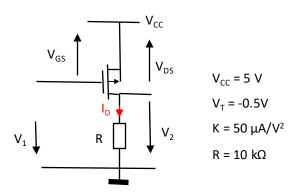

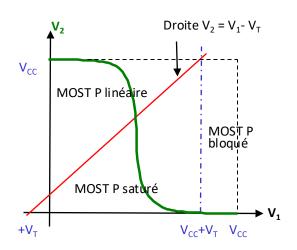

## EXERCICE 2

#### Inverseur logique P-MOS

Calculer et tracer la caractéristique de transfert  $V_2 = f(V_1)$ .

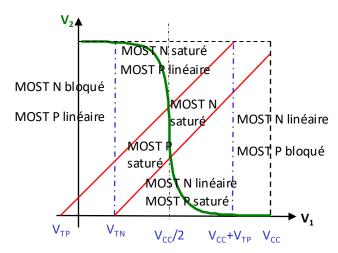

### **EXERCICE 3**

#### Inverseur logique CMOS

Calculer et tracer la caractéristique de transfert  $V_2 = f(V_1)$ .